Source Code

Browse Dynamatic's 2.0 source code. You can download and compile manually the packages.

Dynamatic 2.0 on Github

Dynamatic is an academic, open-source high-level synthesis compiler that produces synchronous dynamically-scheduled circuits from C/C++ code. Dynamatic generates synthesizable RTL which currently targets Xilinx FPGAs and delivers significant performance improvements compared to state-of-the-art commercial HLS tools in specific situations (e.g., applications with irregular memory accesses or control-dominated code). The fully automated compilation flow of Dynamatic is based on LLVM. It is customizable and extensible to target different hardware platforms and easy to use with commercial tools such as Vivado (Xilinx) and Modelsim (Mentor Graphics).

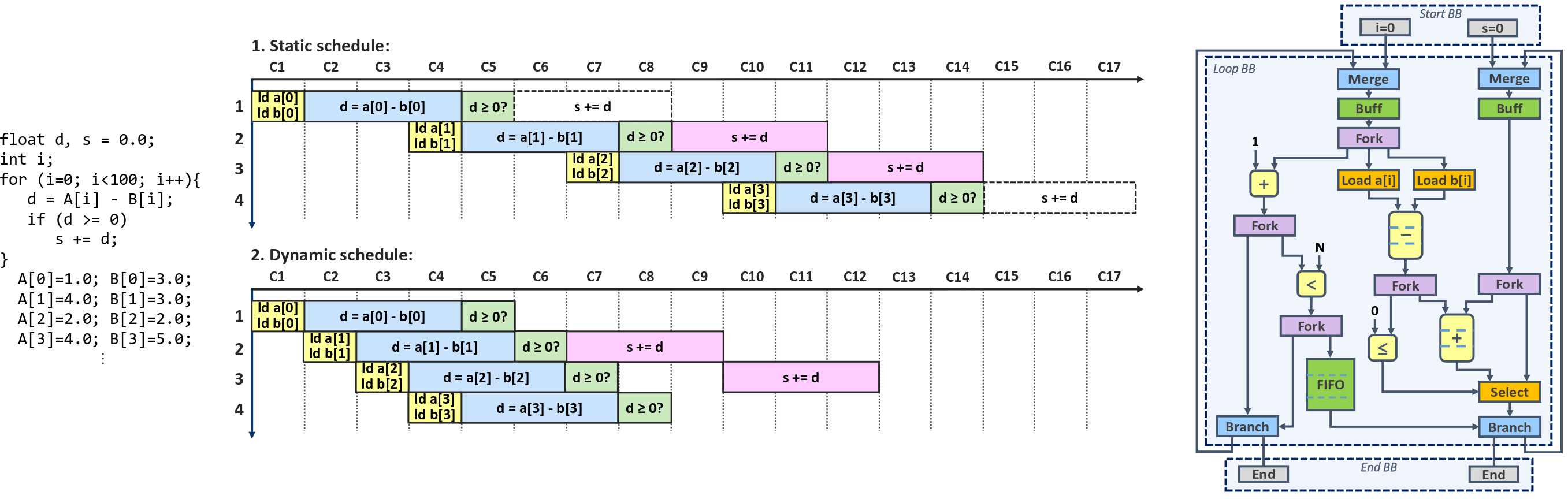

To illustrate the limitations of standard HLS approaches, consider the code on the left of Figure 1. In this loop, there is a control flow decision (if) which depends on the actual data being read from arrays A[ ] and B[ ]. The operation which might take place in a specific iteration (s = s + d) introduces a dependency between iterations and delays the next iteration whenever the condition is true.

When pipelining this loop, a typical HLS tool needs to create a static schedule—that is, a conservative execution plan for the various operations in the loop which is valid in every possible case. Such a schedule is shown on the top of Figure 1: in the example, the condition is true only for the second and third iteration but “space” is reserved in the schedule as if the condition were true everywhere. Obviously, a good schedule is the bottom one: the operations of different iterations are overlapped as much as possible and the parallelism is reduced only when the dependency is actually there (that is, when the addition is executed). This schedule can be achieved by the dynamically scheduled circuit on the right: in this circuit, components exchange data as soon as all conditions for execution are satisfied and the schedule is adapted at runtime to particular data and control outcomes. Such behavior, realized in Dynamatic, is beyond what a statically scheduled HLS tool can achieve.

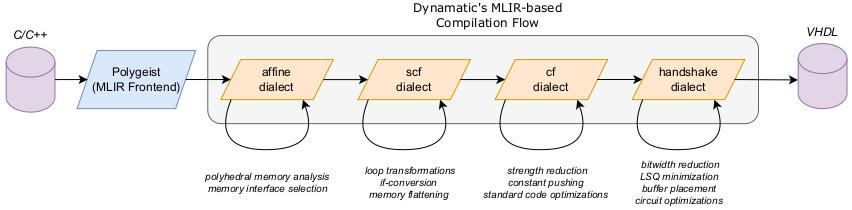

A brand new version of Dynamatic based on the MLIR compiler infrastructure, to take advantage of MLIR’s modularity and reusability. Our new incarnation of Dynamatic puts more emphasis on the richness of features and user-friendliness, and is now more useful for both HLS designers and HLS researchers.

Dynamatic 2.0 is released as open source under Apache 2.0 license.

Three different version are available for download: source code, auto-install package, and the pre-installed virtual machine.

Browse Dynamatic's 2.0 source code. You can download and compile manually the packages.

Dynamatic 2.0 on Github

Download and install automatically Dynamatic 2.0 on your machine.

Dynamatic 2.0 Installer

Download the virtual machine with Dynamatic 2.0 pre-installed.

Dynamatic 2.0 VM

For full and updated list of publications please visit LAP and Dynamo publications websites

Jiahui Xu, Emmet Murphy, Jordi Cortadella and Lana Josipović. Eliminating Excessive Dynamism of Dataflow Circuits Using Model Checking. In Proceedings of the 31st ACM/SIGDA International Symposium on Field Programmable Gate Arrays, Monterey, Calif., February 2023.

Ayatallah Elakhras, Riya Sawhney, Andrea Guerrieri, Lana Josipović and Paolo Ienne. Straight to the Queue: Fast Load-Store Queue Allocation in Dataflow Circuits. In Proceedings of the 31st ACM/SIGDA International Symposium on Field Programmable Gate Arrays, Monterey, Calif., February 2023.

Jiantao Liu, Carmine Rizzi and Lana Josipovic. Load-Store Queue Sizing for Efficient Dataflow Circuits. In Proceedings of the 2022 International Conference on Field Programmable Technology, Hong Kong, December 2022.

Carmine Rizzi, Andrea Guerrieri, Paolo Ienne and Lana Josipovic. A Comprehensive Timing Model for Accurate Frequency Tuning in Dataflow Circuits. 32nd International Conference on Field Programmable Logic and Applications, Belfast, United Kingdom, September 2022.

Jianyi Cheng, Lana Josipović, George Constantinides and John Wickerson. Dynamic Inter-Block Scheduling for HLS. 32nd International Conference on Field Programmable Logic and Applications, Belfast, United Kingdom, September 2022.Best Paper Award Nominee.

Ayatallah Elakhras, Andrea Guerrieri, Lana Josipovic and Paolo Ienne. Unleashing Parallelism in Elastic Circuits with Faster Token Delivery. 32nd International Conference on Field Programmable Logic and Applications, Belfast, United Kingdom, September 2022.Best Paper Award Nominee.

Lana Josipović, Axel Marmet, Andrea Guerrieri, and Paolo Ienne. Resource sharing in dataflow circuits. In Proceedings of the 30th IEEE International Symposium on Field-Programmable Custom Computing Machines, New York City, NY, May 2022. Best Paper Award Nominee.

Lana Josipović, Shabnam Sheikhha, Andrea Guerrieri, Paolo Ienne, and Jordi Cortadella. Buffer placement and sizing for high-performance dataflow circuits. ACM Transactions on Reconfigurable Technology and Systems (TRETS). 15(1):1–32, November 2021.

Lana Josipović, Andrea Guerrieri, and Paolo Ienne. Synthesizing General-Purpose Code Into Dynamically Scheduled Circuits. IEEE Circuits and Systems Magazine, Special Issue FPGA Evolution, Volume 21, Number 2 Second Quarter 2021

Lana Josipović, Andrea Guerrieri, and Paolo Ienne. From C/C++ code to high-performance dataflow circuits. IEEE Transactions on Computer-Aided Design (TCAD). August 2021.

Lana Josipović, Andrea Guerrieri, and Paolo Ienne. Dynamatic: From C/C++ to Dynamically-Scheduled Circuits. Invited tutorial. In Proceedings of the 28th ACM/SIGDA International Symposium on Field Programmable Gate Arrays, Seaside, Calif., February 2020

Lana Josipović, Shabnam Sheikhha, Andrea Guerrieri, Paolo Ienne, and Jordi Cortadella. Buffer placement and sizing for high-performance dataflow circuits. In Proceedings of the 28th ACM/SIGDA International Symposium on Field Programmable Gate Arrays, pages 186–96, Seaside, Calif., February 2020. Best Paper Award.

Jianyi Cheng, Lana Josipović, George A. Constantinides, Paolo Ienne, and John Wickerson. Combining dynamic & static scheduling in high-level synthesis. In Proceedings of the 28th ACM/SIGDA International Symposium on Field Programmable Gate Arrays, pages 288–98, Seaside, Calif., February 2020.

Lana Josipović, Atri Bhattacharyya, Andrea Guerrieri and Paolo Ienne. Shrink It or Shed It! Minimize the Use of LSQs in Dataflow Designs. In Proceedings of the 2019 International Conference on Field Programmable Technology, Tianjin, December 2019.

Lana Josipović, Andrea Guerrieri, and Paolo Ienne. Speculative dataflow circuits. In Proceedings of the 27th ACM/SIGDA International Symposium on Field Programmable Gate Arrays, pages 162-71, Seaside, Calif., February 2019.

Lana Josipović, Radhika Ghosal, and Paolo Ienne. Dynamically scheduled high-level synthesis. In Proceedings of the 26th ACM/SIGDA International Symposium on Field Programmable Gate Arrays, pages 127-36, Monterey, Calif., February 2018. Best Paper Award Nominee.

Lana Josipović, Philip Brisk, and Paolo Ienne. From C to elastic circuits. In Proceedings of the 51st Annual Asilomar Conference on Signals, Systems, and Computers, pages 121-25, Pacific Grove, Calif., October 2017.

Lana Josipović, Philip Brisk, and Paolo Ienne. An out-of-order load-store queue for spatial computing. In Proceedings of the International Conference on Compilers, Architectures, and Synthesis for Embedded Systems, Seoul, Korea, October 2017. See ACM TECS paper below. Best Paper Award Nominee.

Lana Josipović, Philip Brisk, and Paolo Ienne. An out-of-order load-store queue for spatial computing. ACM Transactions on Embedded Computing Systems (TECS), 16(5s):125:1–125:19, September 2017.

Dynamatic has been developed at Processor Architecture Laboratory, at EPFL, Lausanne, Switzerland, and

at Dynamo Research Group at ETH Zurich, Zurich, Switzerland.

The Dynamatic team invites the community to try out our Dynamically Scheduled High-Level Synthesis compiler.

Interested to contribute? Write us an email. we will be glad to reply to your questions!

Atri Bhattacharyya, Philip Brisk, Jianyi Cheng, George A. Constantinides, Jordi Cortadella, Ayatallah Elakhras, Radhika Ghosal, Jiantao Liu, Axel Marmet, Emmet Murphy, Carmine Rizzi, Riya Sawhney, Shabnam Sheikhha, John Wickerson, Jiahui Xu.